|

|

楼主 |

发表于 2022-3-4 09:13:12

|

显示全部楼层

前辈您好,我把testbench改成下面的,但还是不行

`timescale 1ns/100ps

//`define CLOCK_PERIOD 10 //单位ns

//`define CLOCK_FREQ 100 //100_000_000

module flash_led_top_tb();

reg rst;

reg sw0;

wire [15:0] led;

wire [3:0] an; //4个数码管使能信号

wire [6:0] seven_segment;

parameter CLOCK_PERIOD = 10;

parameter CLOCK_FREQ = 100;

// Generate 100 MHz clock

reg clk = 0;

// always #(`CLOCK_PERIOD/2) clk = ~clk;

always # CLOCK_PERIOD clk = ~clk;

flash_led_top #( .CYCLES_PER_SECOND(CLOCK_FREQ) )

inst_flash_led_top(

.clk( clk ),

.rst( rst ),

.sw0( sw0 ),

.led( led ),

.an( an ),

.seven_segment( seven_segment )

);

initial begin

rst = 1'b0;

sw0 = 1'b0;

#10;

rst = 1'b1;

#10;

rst = 1'b0;

repeat(20 * CLOCK_FREQ) # CLOCK_PERIOD; //20次后改变位移方向

sw0 = 1'b1;

end

endmodule

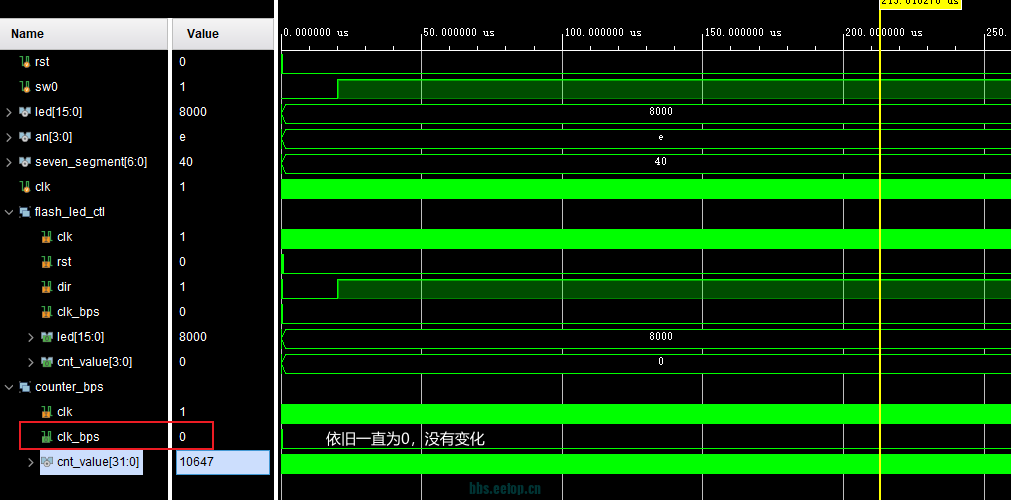

这是布线后定时仿真的截图

|

|

/2

/2