|

|

马上注册,结交更多好友,享用更多功能,让你轻松玩转社区。

您需要 登录 才可以下载或查看,没有账号?注册

×

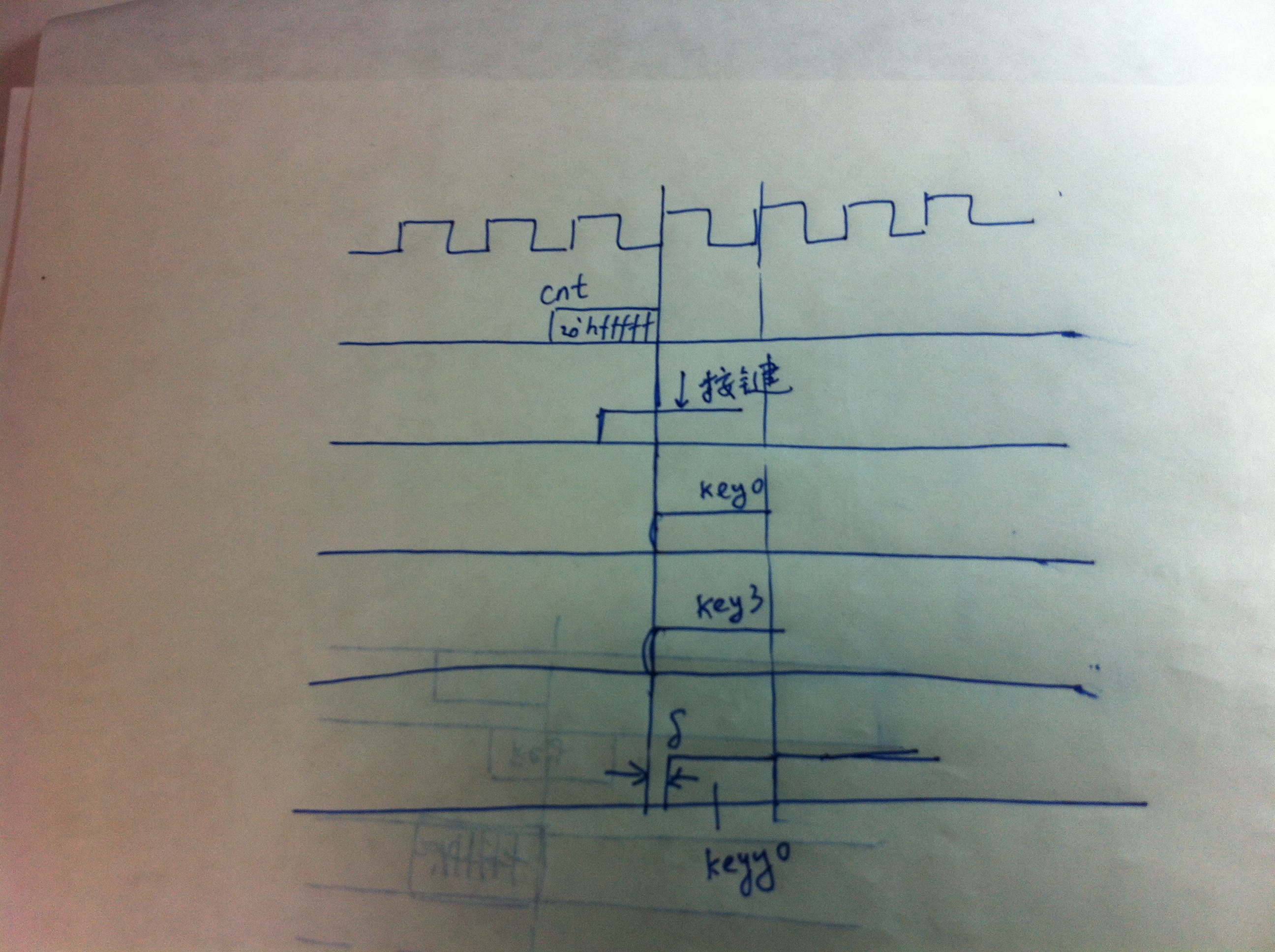

这是我在网上搜到的消抖电路verilog代码

reg key0, key1, key2, key3;

reg [19:0] cnt;

wire keyy0;

always @(posedge clk, negedge rst)

begin

if(!rst)

begin

key0<=1;

key1<=1;

end

else

begin

key0<=indata;

key1<=key0;

end

end

always @(posedge clk, negedge rst)

begin

if(!rst) cnt<=0;

else if(keyy0) cnt<=0;

else cnt<=cnt+1;

end

assign keyy0=key1&(~key0);

always @(posedge clk, negedge rst)

begin

if(!rst)

begin

key2<=1;

end

else if(cnt==20'hfffff)

begin

key2<=indata;

end

end

always @(posedge clk, negedge rst)

begin

if(!rst)

begin

key3<=1;

end

else

begin

key3<=key2;

end

end

assign outdata=key3&(~key2);

我怎么感觉有点问题啊

如果出现了下面的时序,结果不就错了吗,求解,谢谢

|

|

|

/2

/2