|

|

|

马上注册,结交更多好友,享用更多功能,让你轻松玩转社区。

您需要 登录 才可以下载或查看,没有账号?注册

×

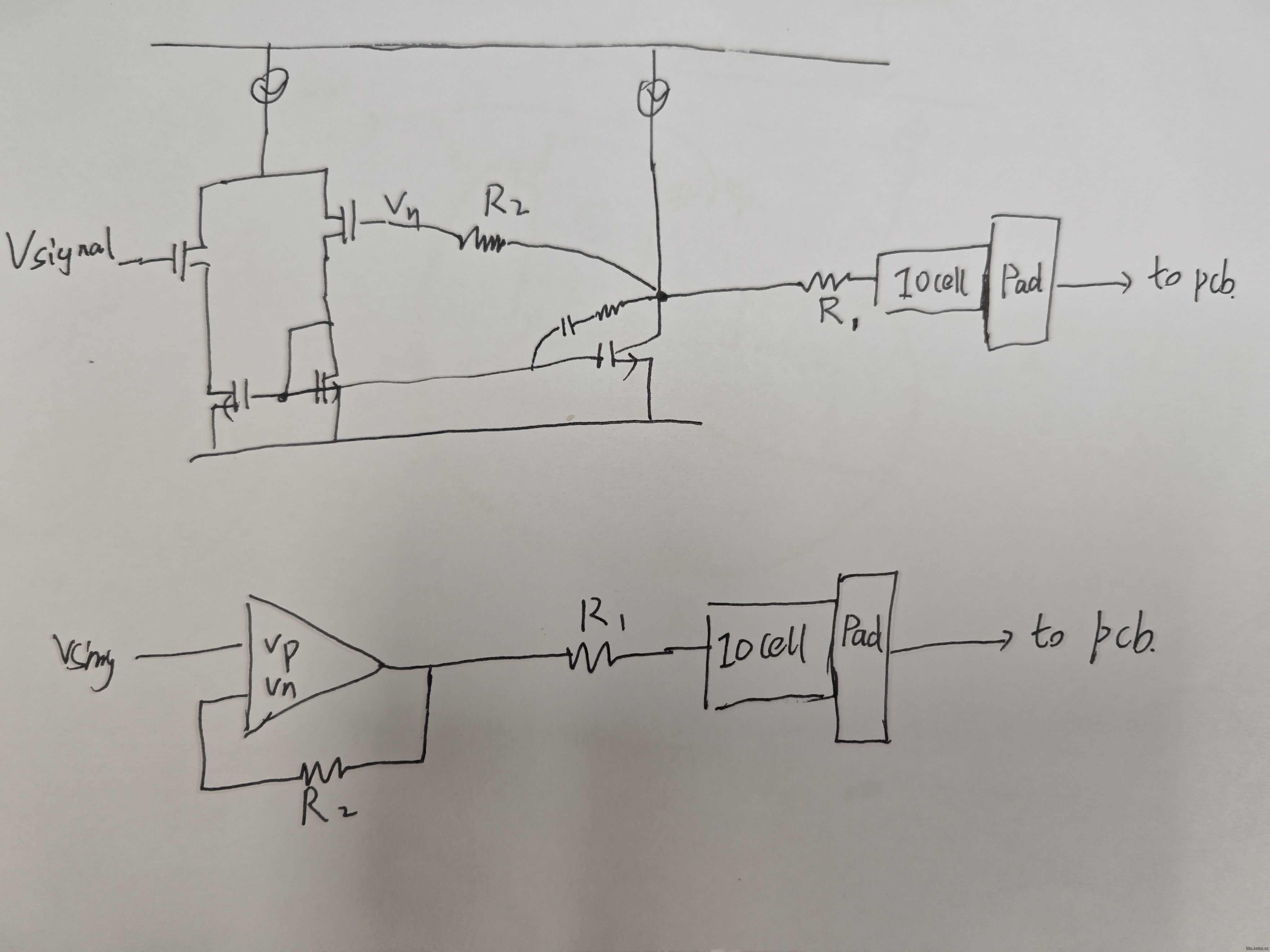

fig1.电阻加在何处?

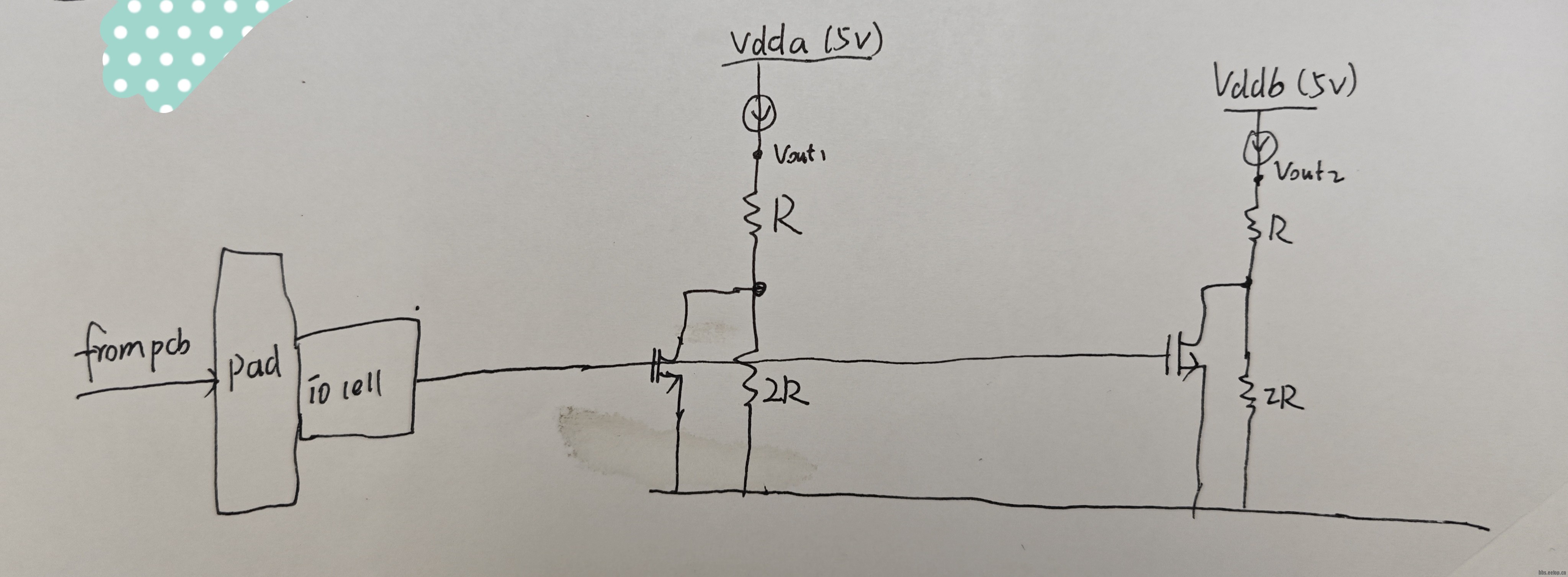

fig2.有没有esd风险

fig1 这种输出buffer,如果加esd电阻的话,加在哪里比较好呢?是r1比较好还是r2,还是必须都加上?我个人感觉r1可以把里面的mos的drain和gate都保护起来了? 还有图二这种,这两个电路是两个不同的测试模块的trim电路,虽然两个trim电路是不同电源pad供电,但是供电电压都是5v,唯一的区别可能是我流片之后测试其中一个模块的时候可能把令一个测试电路关掉,也就是不给它供电,这个算不算跨电源域,有没有esd风险?

fig1 这种输出buffer,如果加esd电阻的话,加在哪里比较好呢?是r1比较好还是r2,还是必须都加上?我个人感觉r1可以把里面的mos的drain和gate都保护起来了? 还有图二这种,这两个电路是两个不同的测试模块的trim电路,虽然两个trim电路是不同电源pad供电,但是供电电压都是5v,唯一的区别可能是我流片之后测试其中一个模块的时候可能把令一个测试电路关掉,也就是不给它供电,这个算不算跨电源域,有没有esd风险?

|

|

/1

/1