|

|

马上注册,结交更多好友,享用更多功能,让你轻松玩转社区。

您需要 登录 才可以下载或查看,没有账号?注册

×

本帖最后由 fanny_haiyun 于 2014-7-2 15:20 编辑

刚开始使用chipscope, 有很多地方还不是特别明白,忘各位前辈不吝赐教

(1)我的设计大致思路如下:

两块FPGA通过导线连接,进行通信

FPGA1 FPGA2

clk_out ------> clk_in

data_out[1:0] ------> data_in[1:0]

en_out ------> en_in

clk_in <------ clk_out

data_in[1:0] <------ data_out[1:0]

en_in <------ en_out

(2) 通过chipscope分别取抓取两块板子上的信号,发现:所有的output均正确,但是input信号会有不太期望的信号出现,具体如下:

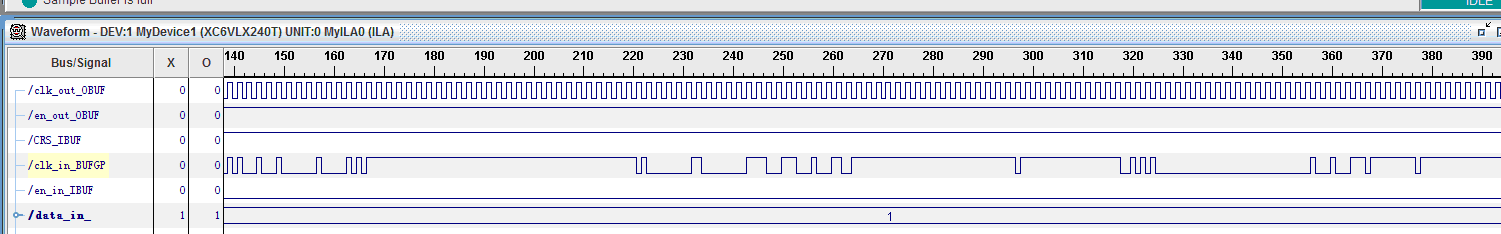

a. 用100M的时钟去抓取50M的clk_in, 出现以下现象:

(clk_in有一段时间的高电平,或者低电平)

问题:在确定clk_out正确的前提下,clk_in为何会产生这样的现象呢?是因为clk_in是时钟,所以会在传输过程中产生错误吗?还是跟我的时钟频率有关系。

b. (感觉自己的截图有问题)

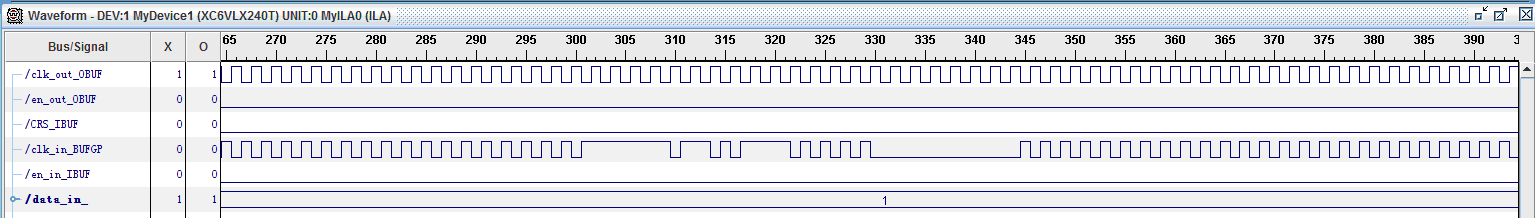

用100M去采样en_in信号时,会出现短小的脉冲高电平(理想情况下是不会产生的,en_in有效时一定是较长的一段高电平)

关于这个问题的深入实验表明:(以采样FPGA2上的信号来举例)

当拔掉FPGA2上连接clk_in的线,en_in就机会不会产生这样的短脉冲信号;

当拔掉FPGA2上连接的clk_out的线,en_in还是会产生这样的脉冲信号;

进一步确认:在FPGA2中把clk_in和clk_out引脚挑换,en_in的短脉冲还是只和clk_in信号有关

问题:对于上述现象的产生原因我没有想通。

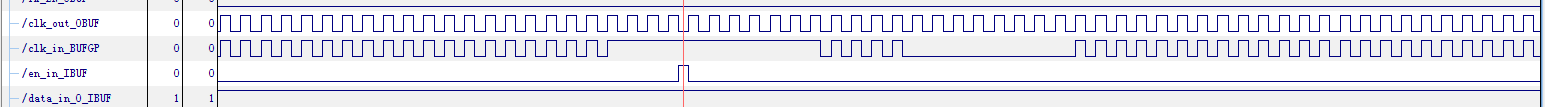

c. 【补充】我现在的数据会出错,主要原因在于en_in会产生小脉冲(本不应该产生),尤其是在en_out有效期间,en_in产生小脉冲的情况特别严重(chipscope波形看起来类似于是时钟),我尝试用两级D触发器来过滤这个毛刺,但是效果不好,我想是因为毛刺过于多的原因。

这种脉冲会让我检测到错误的en_in上升沿,响应的数据处理就会有错。我认为主要在于两块板子的连线上,数据会产生干扰,不知道能否有什么办法可以减少这种情况。 |

-

clk_in不稳定

-

clk_in不稳定

-

en_in出现短脉冲

|

/2

/2