|

|

马上注册,结交更多好友,享用更多功能,让你轻松玩转社区。

您需要 登录 才可以下载或查看,没有账号?注册

×

本帖最后由 禅师1988 于 2012-9-4 16:07 编辑

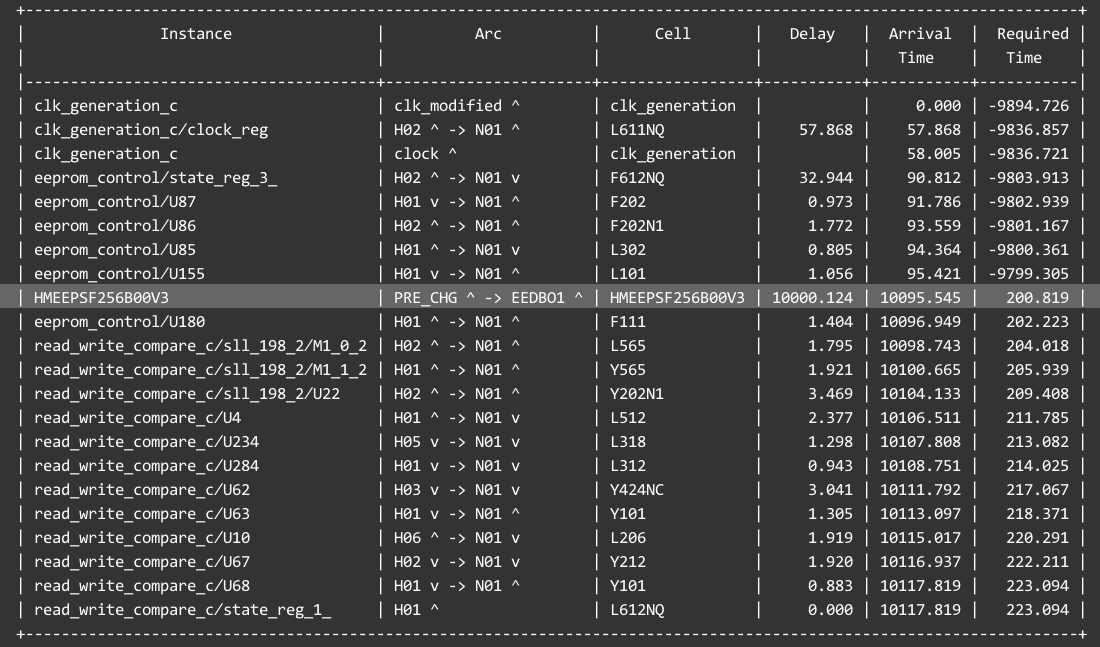

设计中包含一个EEPROM,用DC综合以及astro布局布线都没有时序问题,但是用encounter就显示eeprom的延时过大,

encounter时序分析如下:

可见eeprom的PRE_CHG到EEDBO1的延时很大,而我的时钟周期只有140,造成严重违例,而从lib中的信息来看,这个延时信息没错啊,我的问题是为什么DC和astro中都没有报错,即为什么没有考虑eeprom这个延时??

下面是eeprom的lib中的信息:

pin(EEDBO1) {

direction : output ;

function : " PRE_CHG " ;

capacitance : 0.000000 ;

max_capacitance : 0.714032 ;

timing() {

related_pin : "PRE_CHG" ;

cell_rise(Table1) {

values(\

"10000.019531, 10000.059570, 10000.089844, 10000.169922",\

"10000.330078, 10000.370117, 10000.400391, 10000.480469",\

"10001.580078, 10001.629883, 10001.660156, 10001.730469",\

"10003.150391, 10003.190430, 10003.219727, 10003.299805",\

"10004.709961, 10004.759766, 10004.790039, 10004.860352"\

);

}

rise_transition(Slew1) {

values(\

"4.482940, 8.836245"\

);

}

cell_fall(Table1) {

values(\

"10000.019531, 10000.070312, 10000.099609, 10000.169922",\

"10000.349609, 10000.400391, 10000.429688, 10000.500000",\

"10001.639648, 10001.690430, 10001.719727, 10001.790039",\

"10003.250000, 10003.299805, 10003.330078, 10003.400391",\

"10004.870117, 10004.919922, 10004.950195, 10005.019531"\

);

}

fall_transition(Slew1) {

values(\

"3.214440, 6.280863"\

);

}

}

} |

|

/2

/2