|

|

马上注册,结交更多好友,享用更多功能,让你轻松玩转社区。

您需要 登录 才可以下载或查看,没有账号?注册

×

module top_module(

input clk,

input in,

input reset, // Synchronous reset

output [7:0] out_byte,

output done

); //

parameter idle=0,start=1,data=2,stop=3,err=4;

reg [2:0]state;

reg [2:0]cnt;

reg [7:0]buff;

always @(posedge clk)

begin

if(reset)

begin state<=idle;cnt<=0;buff<=0;end

else

case (state)

idle:state<=in?idle:start;

start: state<=data;

data:begin

state<=(cnt<7)?data in?stop:err); in?stop:err);

cnt<=(cnt<7)?(cnt+1):0;

buff<=(cnt<7)?{in,buff[7:1]}:buff;

end

stop:state<=in?idle:start;

err:state<=in?idle:err;

default:state<=idle;

endcase

end

assign done=(state==stop);

assign out_byte=(state==stop)?buff:0;

endmodule

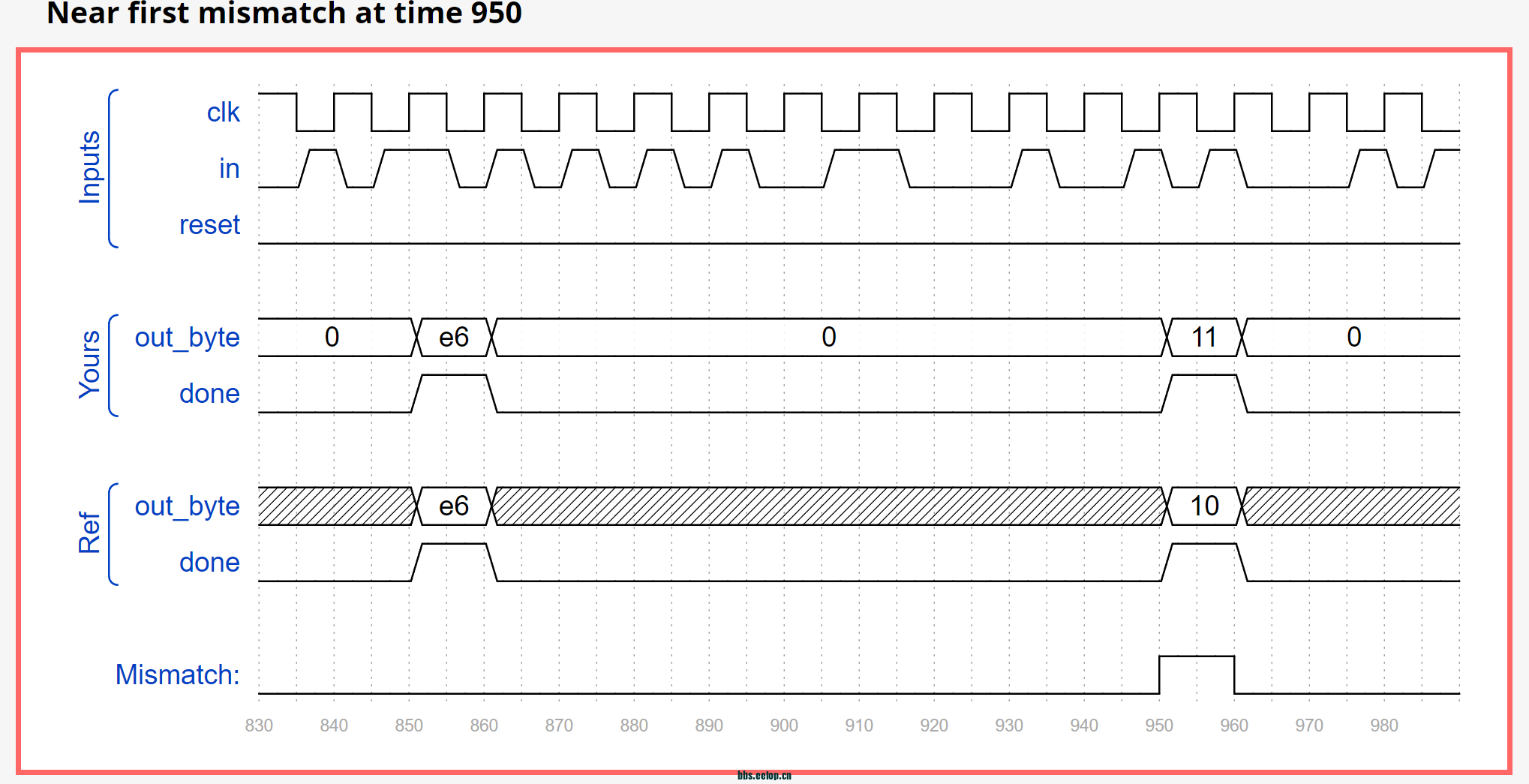

在hdlbits上仿真,out_byte有问题,

求大佬指点一下,data状态的 这句串并转换 buff<=(cnt<7)?{in,buff[7:1]}:buff;有什么问题吗,看了好久都不明白这句错在哪里,求大佬指教

求大佬指点一下,data状态的 这句串并转换 buff<=(cnt<7)?{in,buff[7:1]}:buff;有什么问题吗,看了好久都不明白这句错在哪里,求大佬指教

|

|

/2

/2