日志

多周期路径

| |

0. 多周期路径

一般情况下数据在任意时钟沿发射,在下一个时钟沿被捕获,但是有时设计者需要延迟几个时钟周期data才被捕获,这就是多周期路径。

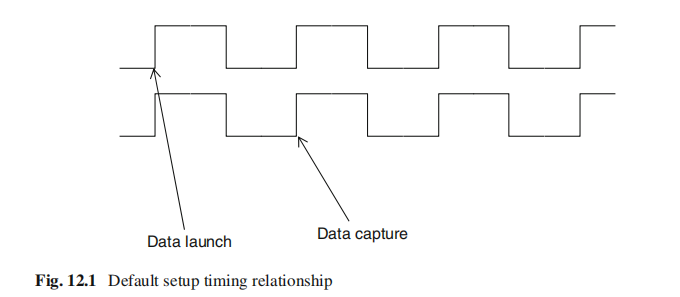

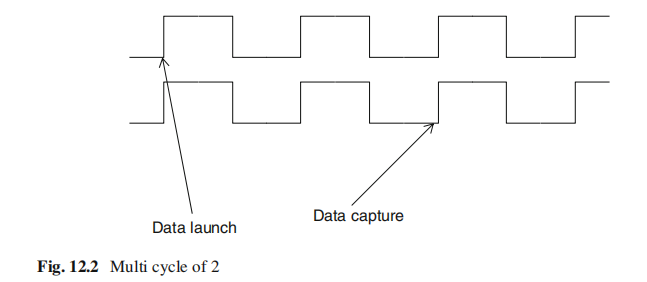

默认的建立时间时序:

多周期的建立时间时序:

1. 发射时钟和捕获时钟相同

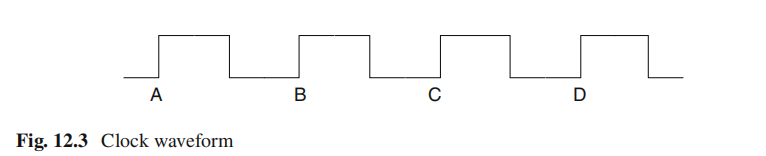

对于上面的时钟,默认是在A沿发射,B沿捕获。在进行建立时间分析时,我们希望在A沿发射数据,在D沿捕获数据,我们可以通过-setup选项,指定多周期路径为3个周期。

1 | set_multicycle_path -setup 3 -from xxx -to xxx |

setup time analysis变成了:Tc-q +Tlogic +Tsetup < 3*T+skew。约束变宽松了。

但是这样的话,在进行hold time分析的时候,工具会对捕获寄存器捕获沿之前的那一个时钟沿,也就是C沿进行hold analysis。这样的话hold time analysis变成了

Tc-q + Tlogic > Thold + 2*T,但这增加了电路的复杂性(需要插入一些buffer来增加延迟),没有必要,通过-hold选项,将hold edge向左移动2个周期

1 | set_multicycle_path -hold 2 -from *** -to *** |

注意:-setup制定多周期路径为N个周期,-hold使hold edge向左移动N-1个周期

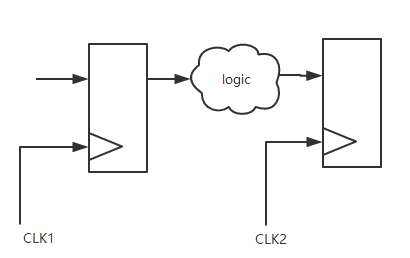

2. 发射时钟和捕获时钟不同

2.1 捕获时钟周期倍长于发射时钟周期

上面例子中发射时钟周期为10ns,捕获时钟周期为20ns。

默认情况下,setup analysis在B沿发射,N沿捕获,组合逻辑路径最大为10ns。对于hold analysis与保持时钟沿没关系,在hold analysis中,可以在A时钟沿发射,M时钟沿捕获,或者在C时钟沿发射,N时钟沿捕获。

因为捕获时钟周期大于采样时钟周期,所以在一个捕获周期中,只能发射一个data。对于在N时钟沿捕获的情况,可以在A或者B时钟沿发射数据。在A发射可以增加额外的10ns的延迟余量。通过-start选项可以声明两个源时钟周期的路径,这使得发射沿从B移动到A。当然要指明是-setup。

1 | set_multicycle_path -setup -start 2 -from xxx -to xxx |

对于hold check有两种情况:

1. A发射M捕获。

2.B发射N捕获。

对于上面两种hold check情况,第二种约束更强,组合逻辑需要增加额外的10ns。我们希望hold check恢复到默认的位置,A发射M捕获(或者B发射N捕获),希望lauch edge从B移动到C,通过-start 和- hold选项。

1 | set_multicycle_path -hold -start 1 -from xxx -to xxx |

-hold指定移动的周期数。

2.2 发射时钟周期倍长于捕获时钟周期

发射时钟周期为20ns,捕获时钟周期为10ns。

默认的setup check是M发射B捕获;hold check是 M发射A捕获。

M发射,希望在C捕获,这样可以增加额外的10ns的延迟裕量。这可以通过-end选项来指定2个目的时钟周期的路径。

1 | set_multicycle_path -setup -end 2 -from xxx -to xxx |

-setup指定路径的周期数,为N

但这会使得hold check变成M发射B捕获,希望它恢复到默认情况,用-end选项指明捕获沿向左移动一个目的时钟周期。

1 | set_multicycle_path -hold -end 1 -from xxx -to xxx |

-hold指定移动的周期数,为N-1

2.3 总结

-start:移动源时钟(发射时钟)沿;

-end :移动目的时钟(捕获时钟)沿;

-setup -start N:向左移动发射时钟沿;

-hold -start N-1:向右移动发射时钟沿;

-setup -end N:向右移动捕获时钟沿;

-hold -end N-1:向左移动捕获时钟沿;

3. examples

3.1 FSM

如上图所示,enable逻辑通过一个N个周期的状态机。那么对于从F1发出的actual data,可以在N个周期内到达F3的输入,所以约束如下:

1 | set_multicycle_path -setup N -end -from Cs -through F1/Q -to Cd <br>set_multicycle_path -hold N-1 -end -from Cs -through F1/Q -to Cd |

3.2 reset

1 2 | set_multicycle_path -fall -from reset_n -setup 3set_multicycle_path -fall -from reset_n -hold 2 |

3.3 Large data path macros

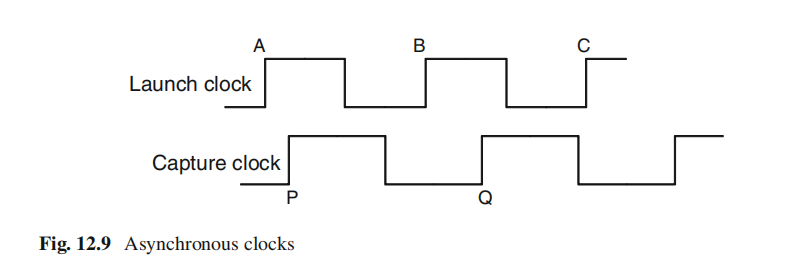

3.4 异步时钟

在跨时钟路径中,一般会生命为fault path,这样STA工具不会对这条路径进行时序分析,那么路径可以有任意大小的delay,但是设计者可能想要约束这一段路径的延迟,如下

1 2 | set_multicycle_path -from [get_clocks C1] -to [get_clocks C2] -setup 2set_multicycle_path -from [get_clocks C1] -to [get_clocks C2] -hold 1 |

原来是在A发射P捕获,但将路径设置为两个捕获周期之后,在A发射Q捕获,组合逻辑延迟扩展了一个捕获周期。这样就将组异步路径合逻辑延迟约束在一个捕获周期多一点。

参考:

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网