日志

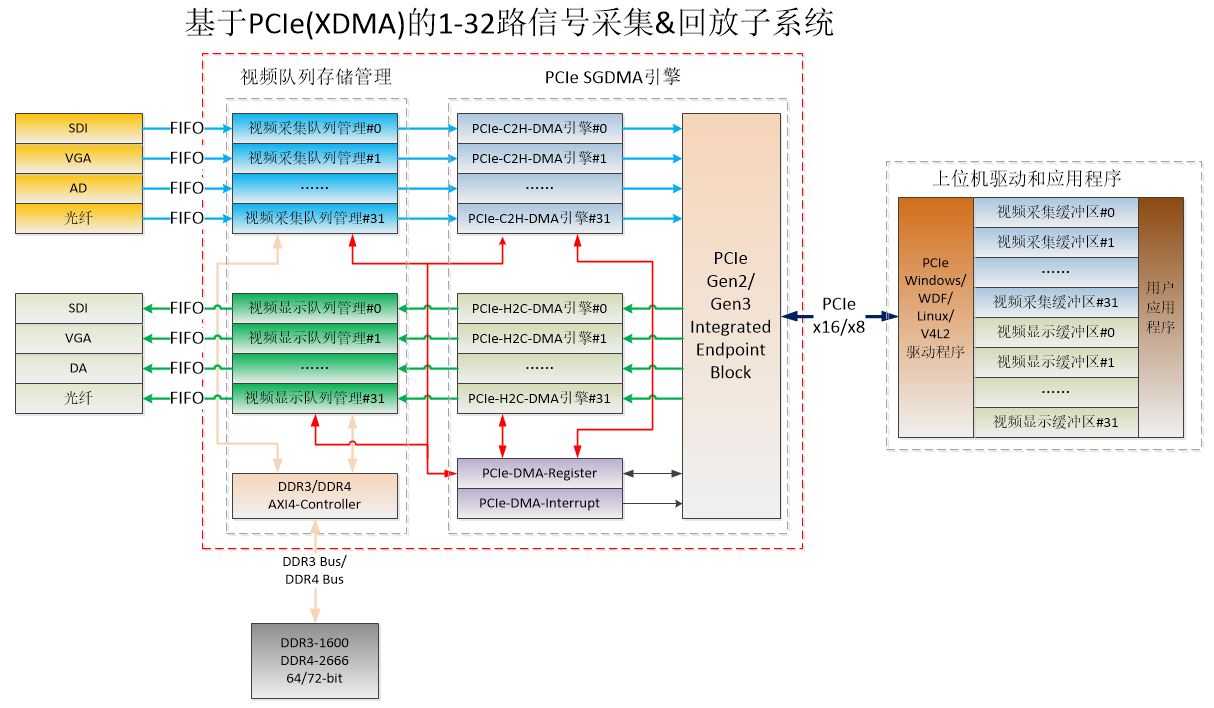

基于PCIe(XDMA)的多路(1-32路)信号采集与回放子系统, 多路视频、AD、光纤等信号,支持PR over PCIe

| |||

基于PCIe(XDMA)的多路(1-32路)信号采集与回放子系统

多路视频、AD、光纤等信号,支持PR over PCIe

1 概述

多路信号采集与回放子系统可以实时采集1-32路视频、AD、光纤等信号,并存储到采集队列中,借助高效的硬实时数据帧出入队列管理和PCIe C2H DMA引擎,将采集到的信号帧实时传递到上位机采集缓冲区。在超带宽视频采集情况下,支持采集丢帧操作,后续视频可以正常采集。

多路信号采集与回放子系统使用高效的PCIe H2C DMA引擎读取上位机显示缓冲区的数据帧,存储到硬实时数据帧回放队列中,并且可以借助外部输入的硬件显示定时脉冲实时访问信号帧回放队列,按照显示定时脉冲输出信号帧。在外部显示定时模式和超带宽显示情况下,支持显示复制帧操作,后续视频可以正常显示。

PCIe DMA引擎基于XDMA,DMA传输效率高,支持4个物理DMA通道,支持PR over PCIe。

对于多路信号采集与回放子系统,在上位机除了使用XDMA驱动,还可以使用标准的Linux V4L2视频驱动,实现多路视频信号的采集和显示工作。

该多路信号采集与回放子系统同样适用于多路高速AD、光纤采集与DA、光纤回放。

2 子系统结构

3 功能特性

1. 支持多种视频接口:SDI、Display Port(DP)、HDMI、DVI、VGA和Camera Link

2. 支持AD、DA、光纤接口

3. 支持DDR3-64bit-1600MHz和DDR4-72bit-2666MHz内存接口

4. 支持PCIe链路速率:PCIe 1.0、PCIe 2.0、PCIe 3.0和PCIe 4.0

5. 支持PCIe链路宽度:PCIe x1、PCIe x2、PCIe x4、PCIe x8和PCIe x16

6. 支持Xilinx器件:7 Series,Ultrascale Series,Ultrascale+ Series

7. 支持多种PCIe驱动:Linux V4L2、Windows WDF和Linux

8. 32个独立的信号采集接口、视频采集队列、PCIe C2H(host-to-card) DMA引擎

9. 32个独立的信号回放接口、视频显示队列、PCIe H2C(card-to-host) DMA引擎

10. 支持全双工32个独立的视频、AD、光纤采集和32个独立的视频、DA、光纤回放

11. 32个信号采集队列参数(队列元素的地址、个数、大小)软件可配置

12. 32个信号显示队列参数(队列元素的地址、个数、大小)软件可配置

13. 支持超带宽视频采集和超带宽视频显示

14. 支持MSI中断,4个DMA中断和16个User中断

15. 支持XDMA,Linux V4L2视频驱动

4 性能指标

1. PCIe 3.0 x16配置下,支持32路光纤信号的采集与回放

2. PCIe 3.0 x16配置下,支持8路4K(3840x2160p)@60Hz的采集与显示

3. PCIe 3.0 x8配置下,支持4路4K(3840x2160p)@60Hz的采集与显示

4. PCIe 3.0 x8配置下,支持8路4K(3840x2160p)@30Hz的采集与显示

5. PCIe 2.0 x8配置下,支持8路FHD(1920x1080p)@60Hz的采集与显示

6. PCIe 2.0 x4配置下,支持8路FHD(1920x1080p)@30Hz的采集与显示

5 用户接口

1. 32路AXI4-Stream或fifo信号采集接口

2. 32路AXI4-Stream或FIFO信号回放接口

3. 外部显示定时脉冲输入

4. User中断输入

5. 信号采集与回放复位输出

6. 信号采集与回放配置输出

可交付资料:

1. 详细的用户手册

2. Design File:Post-synthesis EDIF netlist or RTL Source

3. Timing and layout constraints,Test or Design Example Project

4. 技术支持:邮件,电话,现场,培训服务

全部作者的其他最新日志

- • Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,4通道DMA,1通道IO,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3 ...

- • 高性能PCIe 3.0软核,x1~x16,支持EP/RC,AXI4接口,内置DMA控制器,适用ASIC和FPGA

- • 基于LZO的无损数据压缩IP,高性能32Gbps,适用于FPGA&ASIC

- • Xilinx高性能低延时8通道PCIe-DMA控制器IP,SGDMA,QDMA,CDMA,RDMA, V4L2驱动,高速视频采集, 高速AD采集

- • Xilinx高性能NVMe Host控制器IP,4通道DMA,1通道IO,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和PCIe 4.0

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网