日志

先进工艺下的ESD噩梦:先进制程为何更难防静电?

| ||

在半导体技术沿着摩尔定律高歌猛进之时,一个古老的“幽灵”——静电放电(ESD),正以新的形态卷土重来,成为芯片设计师的终极噩梦。我们赫然发现,在先进制程中,技术越先进,防御静电这一看似简单的任务却变得愈发艰巨。这背后,是一场物理定律与工程极限的残酷碰撞。

图1 .半导体晶体管技术路线

一、 击穿电压的“断崖式”下跌

ESD防护的关键在于,为瞬间的高压脉冲构建一条低阻抗泄放通道,保护脆弱的晶体管栅氧层。然而,在7nm、5nm、3nm等先进制程中,栅氧层已被压缩至区区几个原子层的厚度(约1-2纳米),其本征击穿电压骤降至3-5伏以下。

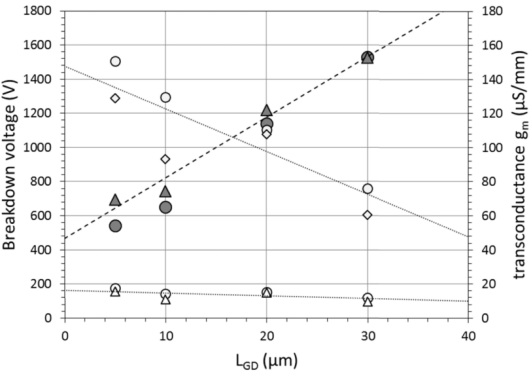

图2.金刚石MESFET的击穿电压和跨导随栅极-漏极长度(L GD)的变化关系,

栅极长度L G = 10和20 μ m。跨导在室温和300°C下测量。

这意味着,过去可能被视为“温和”的静电,其产生的脉冲电压都远超栅氧的承受极限。ESD防护窗口急剧收窄,要求设计者在纳秒量级内将电压钳制在极低水平,容错空间几乎消失。

二、 防护面积与性能的残酷权衡

ESD防护器件的泄放能力需具备足够大的尺寸作为保障。但在先进工艺中,芯片面积寸土寸金。设计师面临一个残酷的“零和游戏”:增加ESD防护面积,就意味着牺牲核心逻辑密度、引入寄生参数、影响最终性能;而缩减防护面积,则无异于让芯片在ESD事件中“裸奔”。在当前设计中,ESD防护已转变为一项必须权衡的关键约束,深刻影响着系统的性能、成本与可靠性。

三、 三维器件结构的“先天脆弱”

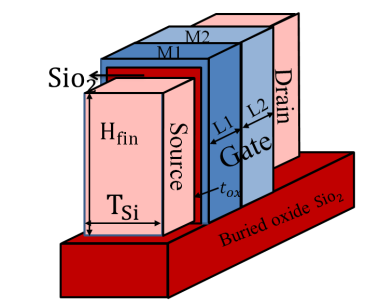

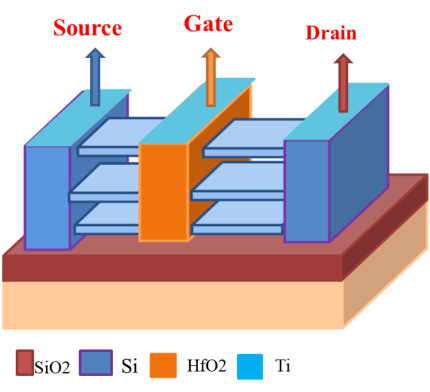

为克服短沟道效应,先进制程普遍采用FinFET(鳍式场效应晶体管)和GAA(环栅晶体管)等三维结构。这些结构在提升性能的同时,也引入了新的ESD噩梦:

图3.DMGFinFET的示意图

图4.GAAMBCFET结构示意图

*热瓶颈:狭窄的“鳍”结构散热极差,ESD大电流下易导致局部热量积聚和熔毁。

*泄放效率降低:三维结构的电流特性使得传统防护器件的触发和泄放效率大打折扣。

*全新失效模式:电流集中等新问题层出不穷,传统设计经验部分失效。

四、 多电压域与系统级协同的复杂危机

现代SoC芯片内部存在多个电压域(如0.8V, 1.8V, 3.3V),它们之间的接口成为ESD冲击的“高危地带”。必须为每个交叉域设计精准的箝位电路,其复杂性呈指数级增长。

同时,系统级ESD威胁日益突出。在更小封装和更高频率下,外部端口的静电脉冲极易通过电磁耦合侵入核心电路,这驱动了设计向更强大的片上ESD防护架构转变。

先进工艺下的ESD防护,已然是一场在物理极限上的“刀尖之舞”。它不再是一个可事后弥补的环节,而是必须从设计伊始就进行全盘考虑、协同优化的核心议题。对于我们而言,这场与静电的战争进入了最残酷、最需要智慧的阶段,每一次工艺的迈进,都意味着我们必须为这艘日益精密的“星舰”,锻造出能在更严酷“雷暴”中穿行的更强“护盾”。

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网