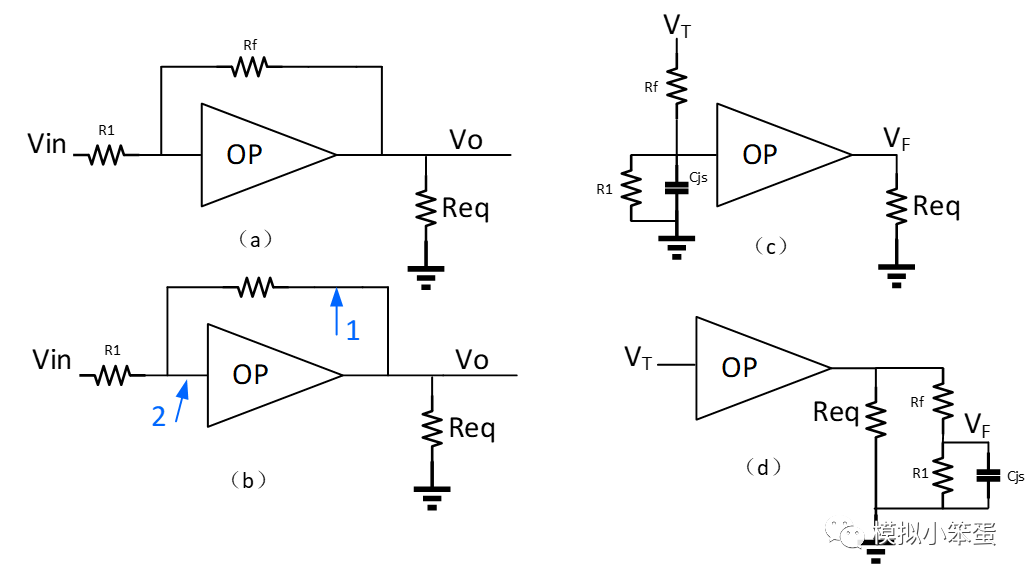

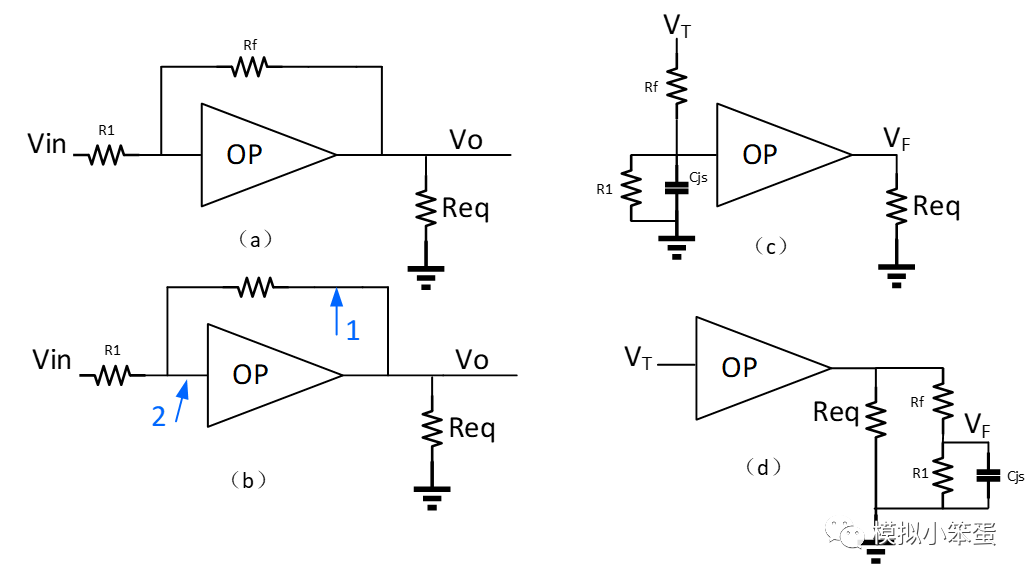

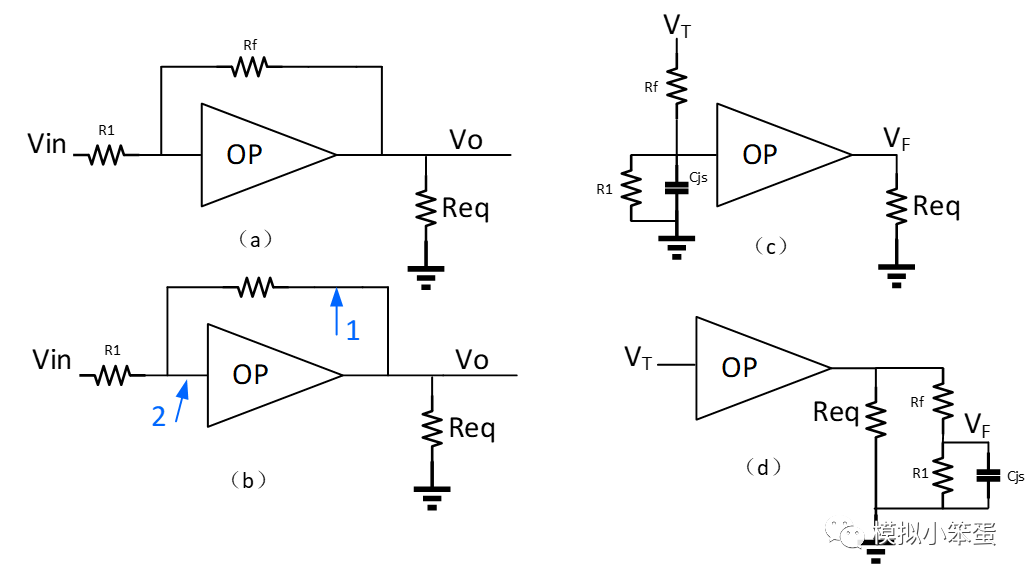

这一篇文章我们主要看下OP闭环电路小信号分析中常见的问题。有时候我们发现stb分析(β=1)的bode图和开环AC仿真的曲线相差很大,且两者的零极点位置、裕度等可能大有不同。探究造成该问题的原因,很有可能是我们在AC开环分析时没有计入反馈元件和输入级寄生电容的影响。更多文章内容,可关注“模拟小笨蛋”微信公众号,定期分享模拟IC设计相关的知识,小技巧。 图1 (a)运放负反馈放大电路(b)存在两处可断环位置(c)第1处断环处理(d)第2处断环处理

图1 (a)运放负反馈放大电路(b)存在两处可断环位置(c)第1处断环处理(d)第2处断环处理

对于图1a所示的电路,我们可以在图1b所示的两处位置断环。图1c和图1d两种断环情况下VF/VT是相同的。需要注意的是图1d,虽然在运放输入端加激励,但在收集到VF的位置仍然加上了寄生Cjs。OP输入级寄生电容Cjs的Cjs包含走线寄生和输入对栅电容的总寄生。可以看到的是,断环后Rf、R1、Cjs也会形成一个极点。不过一般情况下,Cjs比较小,因此带来的影响较小。但如果当Rf、R1取值较大,且输入对管面积很大时Cjs也会随之变大,那么这三者之间形成的极点很可能会严重影响带宽和稳定裕度。因此,电阻值应该往小取值,小的电阻其热噪声影响也较小(4KTR)。Spectre的stb分析会自动计入相关联节点的阻抗和电容,我们再类比下我们AC分析的方式(下图2),这里完全看不到电阻和寄生电容贡献的零极点,也就不难理解为什么文章开篇提到的问题了。

针对上述问题,我认为有两种处理办法:1,利用stb分析方式;2,AC分析时根据上述断环技巧在AC源和OP输入之间插入Rf、R1、Cjs的网络。

对于更复杂的电路,如图3所示的多级级联电路,第二级的闭环输入Rin即为第一级电路的负载,用Req表示。Rin由第二级反馈组件和运放特性决定,Rin也可能影响第一级的带宽和稳定裕度。这个影响是复杂的。有个简单评估的办法就是,我们可以通过仿真法得到第二级的Rin,观察它随频率的响应,借此分析Rin对前级影响。不过,这只是个原则性指导,有时候我们遇到的问题可能比这复杂的多。

更多文章内容,可关注“模拟小笨蛋”微信公众号,定期分享模拟IC设计相关的知识,小技巧。

图1 (a)运放负反馈放大电路(b)存在两处可断环位置(c)第1处断环处理(d)第2处断环处理

图1 (a)运放负反馈放大电路(b)存在两处可断环位置(c)第1处断环处理(d)第2处断环处理

图1 (a)运放负反馈放大电路(b)存在两处可断环位置(c)第1处断环处理(d)第2处断环处理

图1 (a)运放负反馈放大电路(b)存在两处可断环位置(c)第1处断环处理(d)第2处断环处理

/2

/2