日志

芯片ESD失效分析:从认知误区到精准定位的完整解决方案

| ||

在芯片失效案例中,静电放电(ESD)导致的损伤占比超过25%,却常因“无明显物理痕迹”被误判为设计缺陷或批次质量问题。ESD损伤具有微观性与隐蔽性,许多工程师在分析时仅盯着I/O端口测阻值、查外观,难以找到根本原因。本文基于实际案例和失效分析(FA)实践,系统梳理ESD失效的核心逻辑与实操步骤,帮助工程师高效定位真因。

一、ESD失效的常见认知误区

ESD损伤的微观特性易使分析偏离方向,需先纠正以下误区:

常见误区 | 正确认知 |

仅通过I/O端口电性测试判断ESD损伤 | ESD电流可通过电源/地网络、信号链路扩散,需全面检查内部敏感电路(如MOS管栅极、ESD防护二极管、高频信号通路) |

认为“外观无烧痕就不是ESD失效” | 80%以上的ESD损伤是微观级(如栅氧击穿、金属互连层熔断),需高倍镜(≥500倍)或截面分析才能发现 |

直接采信客户提供的“ESD事件记录” | 需亲自复现芯片电性异常,结合客户测试环境(如湿度、防静电措施)交叉验证,排除“伪ESD失效” |

核心原则:分析起点应是“验证失效真实性”,而非直接追溯ESD事件。需通过透射电子显微镜(TEM)或扫描电子显微镜(SEM)排查所有敏感电路。

二、ESD失效分析的实操流程

步骤1:失效验证——确认是否为真ESD失效

拿到疑似ESD失效芯片后,优先完成非破坏性验证:

·基础信息建档:记录芯片型号、生产批次、封装类型(如QFP、BGA)、失效场景;

·外观初检:用光学显微镜(OM)观察引脚氧化、变形、焊锡残留及封装微裂;

·电性参数比对:测试I/O口漏电流(正常≤1μA,损伤后可能达mA级)、电源端短路情况。

关键原则:亲自进行电性验证。曾有客户误判“ESD导致I/O口失效”,实际为电源引脚虚焊。

步骤2:失效定位——多工具组合锁定损伤点

ESD损伤多为“点式扩散”,需组合以下工具精确定位:

·发射显微镜(EMMI):检测芯片内部击穿的微弱光信号,可高效锁定μm级异常区域;

·红外热成像(IRT):捕捉0.1℃温度差异,定位漏电产生的局部热点;

·扫描电子显微镜(SEM):拆封装后观察微观结构,需先完成非破坏性定位。

案例示例:某手机射频芯片失效,EMMI在I/O口附近发现亮点,SEM下观察到金属互连层“飞溅状熔断痕迹”,确认为ESD导致的局部过热损伤。

步骤3:样品制备——避免“二次损伤”

ESD损伤微观结构脆弱,样品制备需注意:

·针对性去封装:陶瓷封装用等离子蚀刻(≤150℃),塑料封装用化学开封;

·截面制备:使用聚焦离子束(FIB)制作nm级精度截面,避免机械切割变形;

·全程防静电:佩戴防静电手腕带(接地电阻≤1MΩ),使用接地工作站。

步骤4:根因分析——追溯ESD注入路径

找到损伤点后,需综合分析:

·损伤形态判断:TEM发现栅氧层变薄或孔洞,可能是ESD电压超防护阈值;SEM见金属层断裂,表明该处流过了远超设计承受能力的强电流(通常由ESD事件导致);

·防护电路排查:测试ESD防护器件的IV特性曲线,检查是否失效(如出现短路、开路或参数显著退化);

·应用场景回溯:确认是否在无防静电环境中操作,或存在热插拔行为。

案例示例:某芯片损伤点在电源端,追溯发现客户测试时热插拔电源,导致ESD从电源端注入。

步骤5:验证与报告——确保“可复现、可落地”

分析完成后需形成闭环:

·失效复现验证:模拟客户场景(如施加HBM 2kV ESD电压),观察是否复现相同损伤;

·输出落地报告:包含损伤点照片、测试数据、ESD注入路径图,并提出改进建议:

对客户:建议增加防静电地板、每日检测防静电手环接地电阻;

对设计端:优化ESD防护电路(如加TVS管)、加厚栅氧层(如从5nm增至8nm)。

三、综合案例:A芯片未上机即失效分析

以芯片的静电损伤(ESD)为例,通过外观检查,I-V曲线测量、x-ray检查、开盖检查、热点分析、去层分析等方法,分析芯片失效的原因及机理,并根据实际提出改善建议。

背景介绍:

终端客户反馈上机测试出现故障,PCB板无法正常运行,交叉验证后锁定为A芯片不良,对A芯片进行阻抗 测量,发现A芯片内部某一二极管部分电路阻抗异常偏低。现进行测试分析,查找失效原因。

分析过程:

1. 外观检查:芯片表面无破损、裂痕或丝印异常;

2. I-V曲线测量:PIN4-PIN5之间呈短路特征;

3. X-ray与开盖检查:未发现内部结构或键合线损伤;

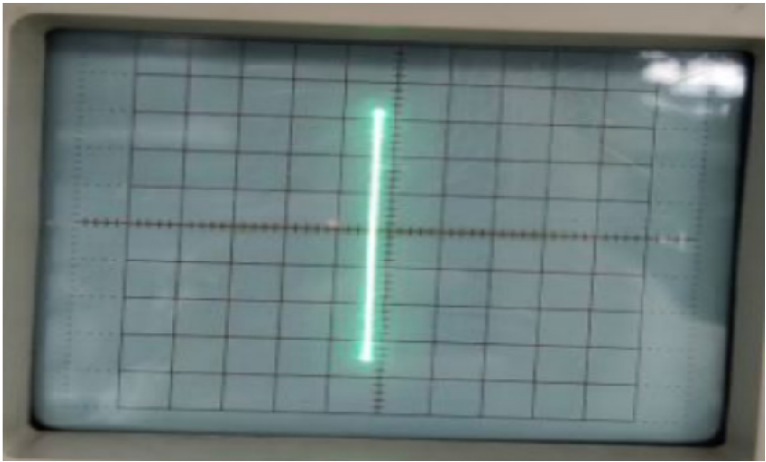

4. 热点分析:使用Thermal对A芯片进行热点定位,定位到PIN4-PIN5附近异常热点;

5. 去层分析:从CT层至SUB层,ESD损伤逐渐加重,SUB层损伤最严重。

6. 结论与建议

A芯片失效的直接原因是ESD导致内部二极管击穿。建议——

客户端:严格规范芯片存储、取放和上电操作流程,确保在有效防静电环境(如佩戴合格接地手环、使用防静电台垫/地板)下进行;

设计端:复查该内部二极管结构及其ESD防护路径设计是否合理,评估其抗ESD能力,考虑优化布局或增加保护强度。

ESD失效分析的核心是“还原从静电产生、注入到芯片失效的完整路径”。需避免“只看局部、依赖经验”的误区,遵循“验证-定位-溯源-闭环”的逻辑,结合多工具分析和场景回溯,才能真正解决问题,降低ESD失效带来的成本损失。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网