日志

3D堆叠的盛宴下,ESD是那颗“定时炸弹”吗?

| ||

由于硅基晶体管的尺寸已逼近原子尺度,其进一步微缩的潜力正受到底层物理规律的严格制约,这使得摩尔定律所预测的演进步伐显著放缓,甚至难以为继。先进封装技术正逐步成为推动半导体产业持续发展、提升芯片性能及集成度的重要途径。通过将多个异构芯粒进行高密度集成,该技术不仅显著提升了算力水平,同时也带来了前所未有的系统复杂性。

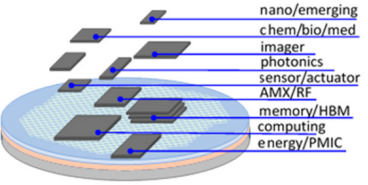

图1 基于HI的SoIC和先进封装的复杂性导致ESD保护设计挑战:(左)用于智能未来SoIC的异构多模层,以及(右)示例CoWoS封装结构

先进封装已从传统的二维平面布线迈向三维立体堆叠,代表技术包括:2.5D/3D封装、扇出型封装(Fan-Out)、系统级封装(SiP)。为顺应电子设备微型化与高性能融合的行业演进趋势,先进封装遭遇了多重挑战:热管理难题、应力与可靠性、信号完整性、测试复杂性、ESD风险升级。其中ESD风险正是所有难题中至关重要且常被低估的一环,其复杂性源于集成本身。

与传统封装相比,先进封装的ESD风险呈指数级增长,根源在于其系统复杂性:

1.电流路径不可预测:ESD电流不再局限于单一芯片内部。放电可能在多个裸片、中介层、基板之间寻找任意路径,可能绕过芯片上精心设计的ESD保护电路,直接冲击脆弱的内联结构。

2.脆弱接口激增:微凸块(μBumps)、TSV、混合键合(Hybrid Bonding)界面等微互连结构,其尺寸仅微米级别,截面积小,自身的电流承受能力(It₂)极低,在ESD大电流面前如同“保险丝”般脆弱。

3.异质集成电位差:集成在一起的各类芯片可能拥有不同的工作电压和接地参考。在纳秒级的ESD事件中,各芯片地电位可能出现瞬时不平衡,形成意外的电位差和放电通路,击穿敏感器件。

4.系统级电容变化:复杂的3D结构改变了整个封装单元的电容特性,极大地影响了充放电设备模型(CDM)ESD事件的发生强度和方式,使其更难预测和防护。

先进封装工艺的ESD主要风险表现为物理失效,常见模式包括:互连熔毁、介质击穿、界面分层。这些失效通常源于人体模型(HBM)、机器模型(MM) 以及,尤其是对先进封装威胁最大的充电设备模型(CDM)——因为在自动化生产 handling 过程中,整个大型、复杂的封装体本身更容易被充电而后快速放电。

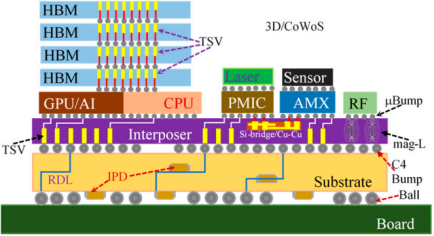

图2 在基于衬垫的典型CDM ESD保护方案中,由于内部随机存储电荷,电荷将通过内部芯片运行,最终放电到接地衬垫,导致随机内部CDM ESD故障

鉴于上述问题,构建一套全新的系统性策略已成为必然要求,而推行系统级ESD协同设计(Co-Design)更是其中的重中之重。该方法要求在项目最初期就引入芯片设计师、封装工程师和OSAT厂商共同参与,将整个封装系统视为统一整体进行ESD防护规划,协同制定接地策略与电流泄放路径。

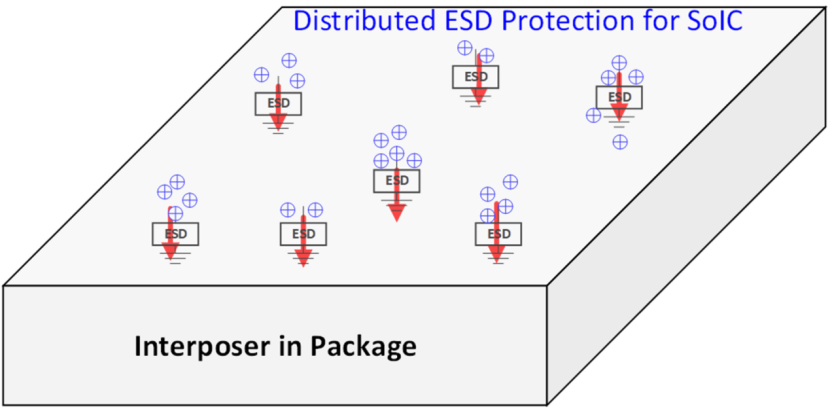

图3 基于插入器的内部分布式CDM ESD保护方法的概念

图4 使用垂直于TSV的ESD保护器件在衬底或中介层中实现内部分布式CDM ESD保护的示意图

预计未来,随着Chiplet技术生态的日益成熟以及三维堆叠层数的持续增多,静电放电(ESD)管理的复杂性将有增无减,其衍生的技术挑战亦将更加严峻。总之,先进封装中的ESD风险是一个典型的“系统问题”,绝不能再用“芯片问题”的旧思路去解决。唯有通过全产业链的协作、创新的设计理念和极致的流程控制,才能驾驭这股强大的静电之力,确保下一代电子产品的可靠与成功。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网